Page 22 - eAC20310_數位邏輯設計 台科大版_課本PDF

P. 22

數位邏輯設計

1 簡單型可程式邏輯元件

簡單型可程式化邏輯元件它是依常用邏輯電路組合設計的架構,由 AND

與 OR 閘(基本邏輯電路,參考第 2-2 節)的二層陣列所組成,經規劃後可執

行被指定的邏輯功能。如可程式唯讀記憶體(programmable read only memory,

PROM)、可程式邏輯陣列(programmable logic array, PLA)、可程式陣列邏輯

(programmable array logic, PAL)與泛型陣列邏輯(generic array logic, GAL)等,

其特性差異如表 1-3 所示。

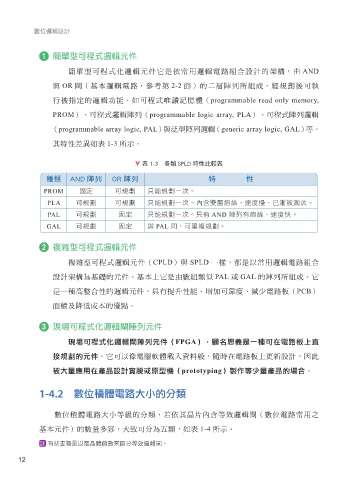

表 1-3 各類 SPLD 特性比較表

種類 AND 陣列 OR 陣列 特 性

PROM ո֛ ̙ྌ ̥ঐྌɓϣf

PLA ̙ྌ ̙ྌ ̥ঐྌɓϣfʫўᕐᄴအകdܓ࿔dʊနଇӖf

PAL ̙ྌ ո֛ ̥ঐྌɓϣf̥Ϟ AND ৬ΐϞအകdܓҞf

GAL ̙ྌ ո֛ ၾ PAL Νd̙ࠠልྌf

2 複雜型可程式邏輯元件

複雜型可程式邏輯元件(CPLD)與 SPLD 一樣,都是以常用邏輯電路組合

設計架構為基礎的元件。基本上它是由數組類似 PAL 或 GAL 的陣列所組成。它

是一種高整合性的邏輯元件,具有提升性能、增加可靠度、減少電路板(PCB)

面積及降低成本的優點。

3 現場可程式化邏輯閘陣列元件

現場可程式化邏輯閘陣列元件(FPGA),顧名思義是一種可在電路板上直

接規劃的元件。它可以像電腦軟體載入資料般,隨時在電路板上更新設計,因此

被大量應用在產品設計實驗或原型機(prototyping)製作等少量產品的場合。

1-4.2 數位積體電路大小的分類

數位積體電路大小等級的分類,若依其晶片內含等效邏輯閘(數位電路常用之

基本元件)的數量多寡,大致可分為五類,如表 1-4 所示。

註 ϞԬࣣᘬ݊˸ཥ౺ࡈᅰԸਜʱഃࣖᜌ፨ཛྷf

12