Page 21 - AB050_8051單晶片實務與應用

P. 21

第二章 MCS-51 系統架構分析 2-5

表 2-1 P3 腳副功能

埠 腳 副 功 能

P3.0 RxD(串列埠輸入端子)

P3.1 TxD(串列埠輸出端子)

P3.2 INT0(外部中斷 0 輸入端子)

P3.3 INT1(外部中斷 1 輸入端子)

P3.4 T0(計時/計數器 0 外部輸入端)

P3.5 T1(計時/計數器 1 外部輸入端)

P3.6 WR(外部資料記憶體 "RAM" 寫入之激發脈波輸出端)

P3.7 RD(外部資料記憶體 "RAM" 讀出之激發脈波輸出端)

3. 第 21~28 腳 P2.0~P2.7

1 一般 I/O 埠

P2 也是內部具有提升電阻的 8 位元雙向 I/O 埠腳。

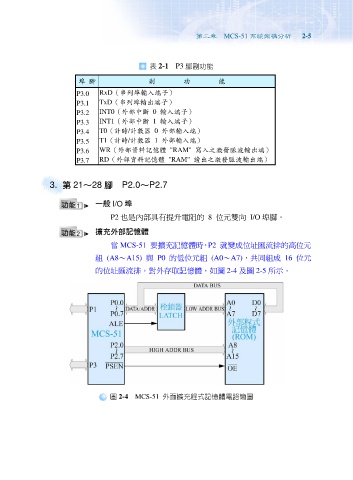

2 擴充外部記憶體

當 MCS-51 要擴充記憶體時,P2 就變成位址匯流排的高位元

組 (A8~A15) 與 P0 的低位元組 (A0~A7),共同組成 16 位元

的位址匯流排,對外存取記憶體,如圖 2-4 及圖 2-5 所示。

圖 2-4 MCS-51 外面擴充程式記憶體電路簡圖