Page 17 - AD02307_數位邏輯含實習升學寶典

P. 17

俪∴塄∡

prop P7-36 7

設正反器的 延遲( 傳遞agation delay )時間為 t P FF , 範例

n

t P Gate

邏輯 閘 的 傳遞 延遲時間為 ,若 漣 波計數器使用

率 f CK

個正反器,則輸入脈波的最高 為 頻

1

f CK

n t P FF + t P Gate

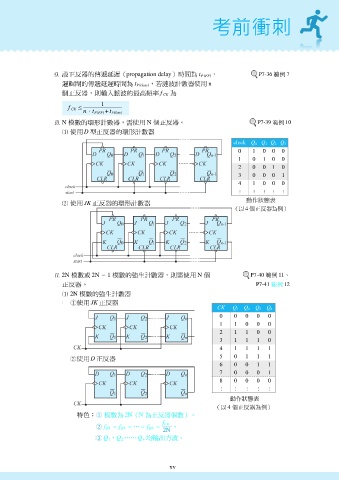

N 模 數的 環形 計數器,需使用 N 個正反器。 P7-39 範例 10

D

使用 型正反器的 環形 計數器

clock Q 0 Q 1 Q 2 Q 3

0 1 0 0 0

1 0 1 0 0

2 0 0 1 0

3 0 0 0 1

4 1 0 0 0

JK 動作狀態表

使用 正反器的 環形 計數器

4

(以 為例)

個

正反器

2N 模 數或 2N 1 模 數的 強生 計數器,則需使用 N 個 P7-40 範例 11 、

P7-41 12

正反器。 範例

2N 模 數的 強生計數器

JK

使用 正反器

CK Q 1 Q 2 Q 3 Q 4

0 0 0 0 0

1 1 0 0 0

2 1 1 0 0

3 1 1 1 0

4 1 1 1 1

D 5 0 1 1 1

使用

正反器

6 0 0 1 1

7 0 0 0 1

8 0 0 0 0

動作狀態表

4

(以 個正反器為例)

2N (N

特 色 : 模 數為 為正反器個數)。

f Q1 = f Q2 = … = f Qn = f CK 。

Q 1 、Q 2 …… Q n 均輸出方波。

xv