Page 15 - AD02307_數位邏輯含實習升學寶典

P. 15

俪∴塄∡

SPLD AND 、OR PROM 、PAL 及PLA

若依 陣列 可程式( 規劃)與 否 來劃分,可分為

P6-69 2

三 者差異 如下: 範例

AND OR

種類 陣列 陣列

PROM 固定 可規劃

PAL 可規劃 固定

PLA 可規劃 可規劃

VHDL

數位 )所 硬 體 描述語言 語言。 與 Verilog-HDL , 先 後成為 IEEE ( 國際 電機電子工程 協

認

可的

會

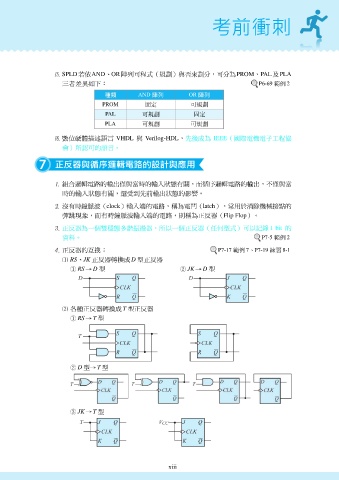

7 ғІᏢᇄඉוᡒᒮႫၯޟ೩ॎᇄᔖҢ

組合邏輯電路的輸出 僅與當時的輸入 狀態 有 關 ,而 循序 邏輯電路的輸出,不 僅 與當

有,

時的輸入 狀態 關 還受到先 前輸出 影響 。 狀態 的

沒 有時鐘脈波( clock )輸入端的電路,稱為電 閂 (latch )常用於消除機 械 接點的

,

彈跳現象 ,而有時鐘脈波輸入端的電路,則稱為正反器( Flip Flop )。

1bit 的 任何 型式)可以 記錄

盪

振

穩態多諧

器,所以一個正反器(

正反器為一個雙

P7-5 2

資料 。 範例

P7-17 7 、P7-19 8-1

正反器的互換: 範例 練習

RS 、JK 正反器轉換成 D 型正反器

RS → D 型 JK → D 型

T

各 種正反器轉換成 型正反器

RS → T 型

D 型→ T 型

JK → T 型

xiii