Page 16 - eAC00920_數位邏輯_課本PDF

P. 16

1-3 邏輯準位

數位系統的信號變化,只有高準位與低準位電壓兩種。高準位電壓稱

為H(high),低準位電壓稱為L(low)。習慣上我們都以 1 與 0 來表示,

即 H =1,L =0。另外也有以事件的「真」、「假」來表達,即 T(true)

表邏輯 1 的高電壓狀態,F(false)表邏輯 0 的低電壓狀態。換句話說,在

數位系統中,信號的變化只有 0 與 1 而已。

1-3.1 邏輯準位分類

至於什麼是「0」、什麼是「1」,在不同的積體電路族系中都各有其

標準。一般都是以輸入小於低準位電壓(input low voltage, V IL)為邏輯 0,

大於高準位電壓(input high voltage, V IH)為邏輯 1。茲列舉說明如下:

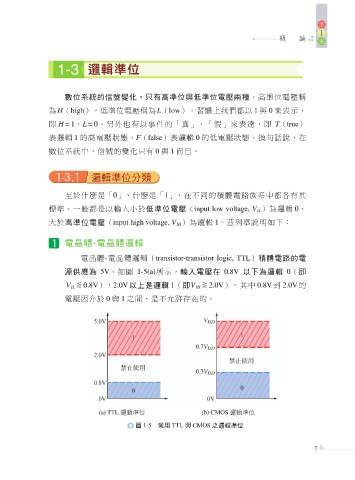

1 電晶體-電晶體邏輯

電晶體-電晶體邏輯(transistor-transistor logic, TTL)積體電路的電

源供應為 5V。如圖 1-5(a)所示,輸入電壓在 0.8V 以下為邏輯 0(即

2.0V)。其中 0.8V 到 2.0V 的

V IL 0.8V),2.0V 以上是邏輯 1(即V IH

電壓因介於 0 與 1 之間,是不允許存在的。

(a) TTL 邏輯準位 (b) CMOS 邏輯準位

圖 1-5 常用 TTL 與 CMOS 之邏輯準位

7