Page 17 - eAC00920_數位邏輯_課本PDF

P. 17

2 互補式金屬氧化物半導體邏輯

傳統 CMOS(complementary metal-oxide semiconductor)IC 的電源供

應有 V DD 與 V SS 兩端,使用時只要 V DD 大於 V SS 在 3~18V 就可正常工

作。如圖 1-5(b)所示,設其電源端電壓 V DD = V DD ,而 V SS =0V,則輸入

0.3 V DD ),0.7 V DD 以上為邏

電壓在 0.3V DD 以下稱為邏輯 0(即 V IL

0.7 V DD )。其中 0.3 V DD 到 0.7 V DD 間之電壓帶是不允許存

輯 1(即 V IH

在的。

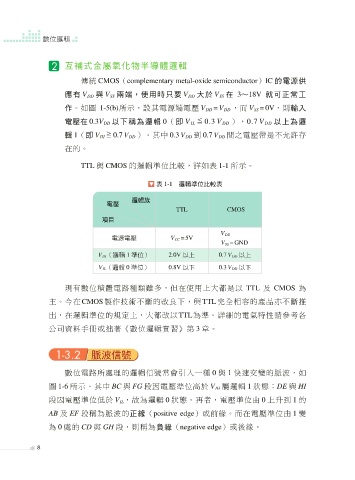

TTL 與 CMOS 的邏輯準位比較,詳如表 1-1 所示。

表 1-1 邏輯準位比較表

邏輯族

電壓

TTL CMOS

項目

V DD

電源電壓 V CC =5V

V SS = GND

V IH(邏輯 1 準位) 2.0V 以上 0.7 V DD 以上

V IL(邏輯 0 準位) 0.8V 以下 0.3 V DD 以下

現有數位積體電路種類雖多,但在使用上大都是以 TTL 及 CMOS 為

主。今在 CMOS 製作技術不斷的改良下,與 TTL 完全相容的產品亦不斷推

出,在邏輯準位的規定上,大都改以TTL為準。詳細的電氣特性請參考各

公司資料手冊或拙著《數位邏輯實習》第 3 章。

1-3.2 脈波信號

數位電路所處理的邏輯信號常會引入一種 0 與 1 快速交變的脈波,如

圖 1-6 所示。其中 BC 與 FG 段因電壓準位高於 V IH 屬邏輯 1 狀態;DE 與 HI

段因電壓準位低於 V IL,故為邏輯 0 狀態。再者,電壓準位由 0 上升到 1 的

AB 及 EF 段稱為脈波的正緣(positive edge)或前緣。而在電壓準位由 1 變

為 0 處的 CD 與 GH 段,則稱為負緣(negative edge)或後緣。

8