Page 18 - eAC00920_數位邏輯_課本PDF

P. 18

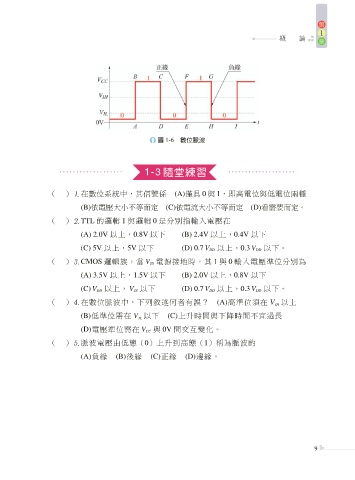

圖 1-6 數位脈波

1-3

( ) 在數位系統中,其信號係 (A)僅具 0 與 1,即高電位與低電位兩種

(B)依電壓大小不等而定 (C)依電流大小不等而定 (D)看需要而定。

( ) TTL 的邏輯 1 與邏輯 0 是分別指輸入電壓在

(A) 2.0V 以上,0.8V 以下 (B) 2.4V 以上,0.4V 以下

(C) 5V 以上,5V 以下 (D) 0.7 V DD 以上,0.3 V DD 以下。

( ) CMOS 邏輯族,當 V SS 電源接地時,其 1 與 0 輸入電壓準位分別為

(A) 3.5V 以上,1.5V 以下 (B) 2.0V 以上,0.8V 以下

(C) V DD 以上, V SS 以下 (D) 0.7 V DD 以上,0.3 V DD 以下。

( ) 在數位脈波中,下列敘述何者有誤? (A)高準位須在 V 以上

IH

(B)低準位需在 V 以下 (C)上升時間與下降時間不宜過長

IL

(D)電壓準位需在 V CC 與 0V 間交互變化。

( ) 脈波電壓由低態(0)上升到高態(1)稱為脈波的

(A)負緣 (B)後緣 (C)正緣 (D)邊緣。

9